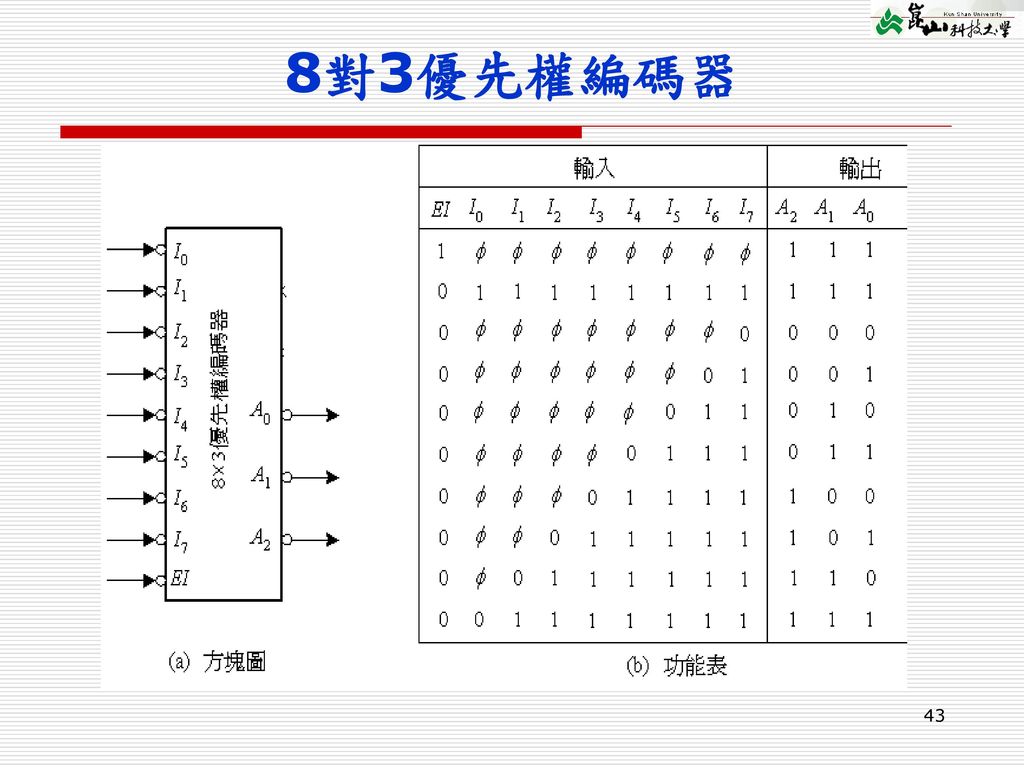

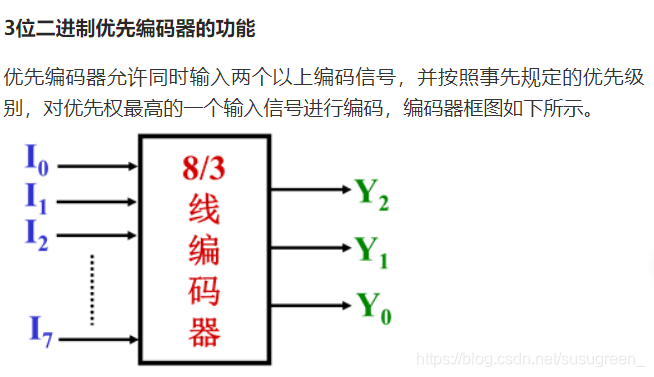

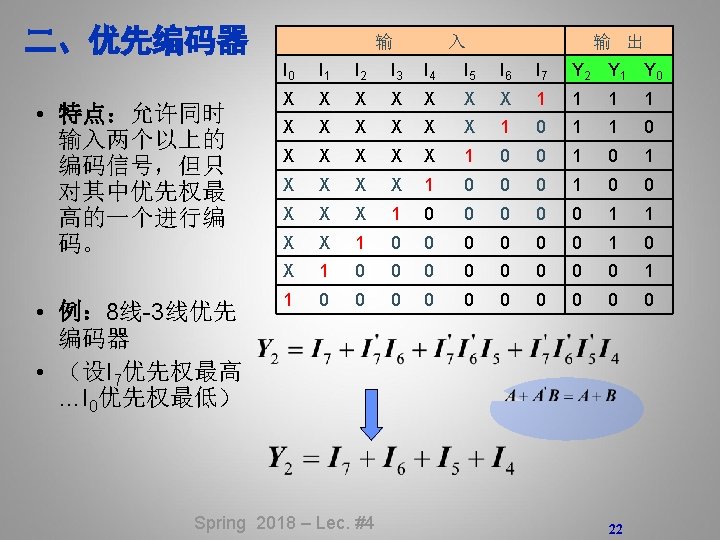

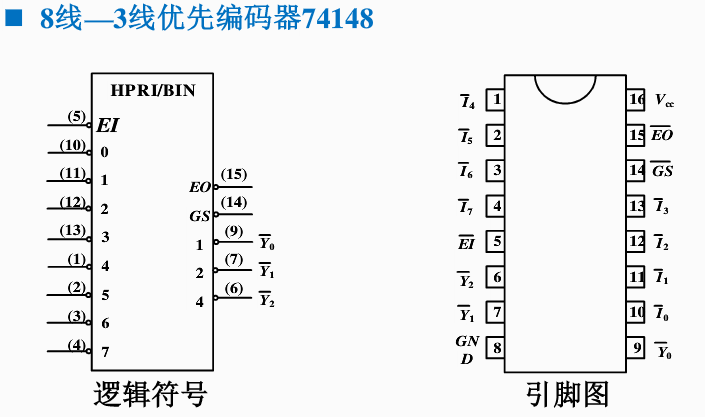

Input 7 0x; VHDL编写线优先编码器 先简单介绍一下什么是"线优先编码器": 线优先编码器由9个输入端和五个输出端组成,允许同时在几个输入端输入信号。当有多个输入信号传入时,只对其中优先权最高的一个输入信号进行编码(输出的二进制代码以反码形式表示) 如图所示: 因此,我们可以进行实体定义: 定义八个输入端(由权低到权高):a,b,c,d,e,f,g,h 定义一个选通输入端_____ ,,74ls148,是8线3线优先编码器,双列16脚封装 ic,外观有标准型和贴片封装类型74ls147是10线4线优先编码器,同样是双列16脚ic 74hc148和74ls148的性能及其区别 _____ 它是个 八线三线 优先级编码器74hc是兼容cmos电平的,供电3~12v ;74ls是兼容ttl电平的,供电45~55v 基本

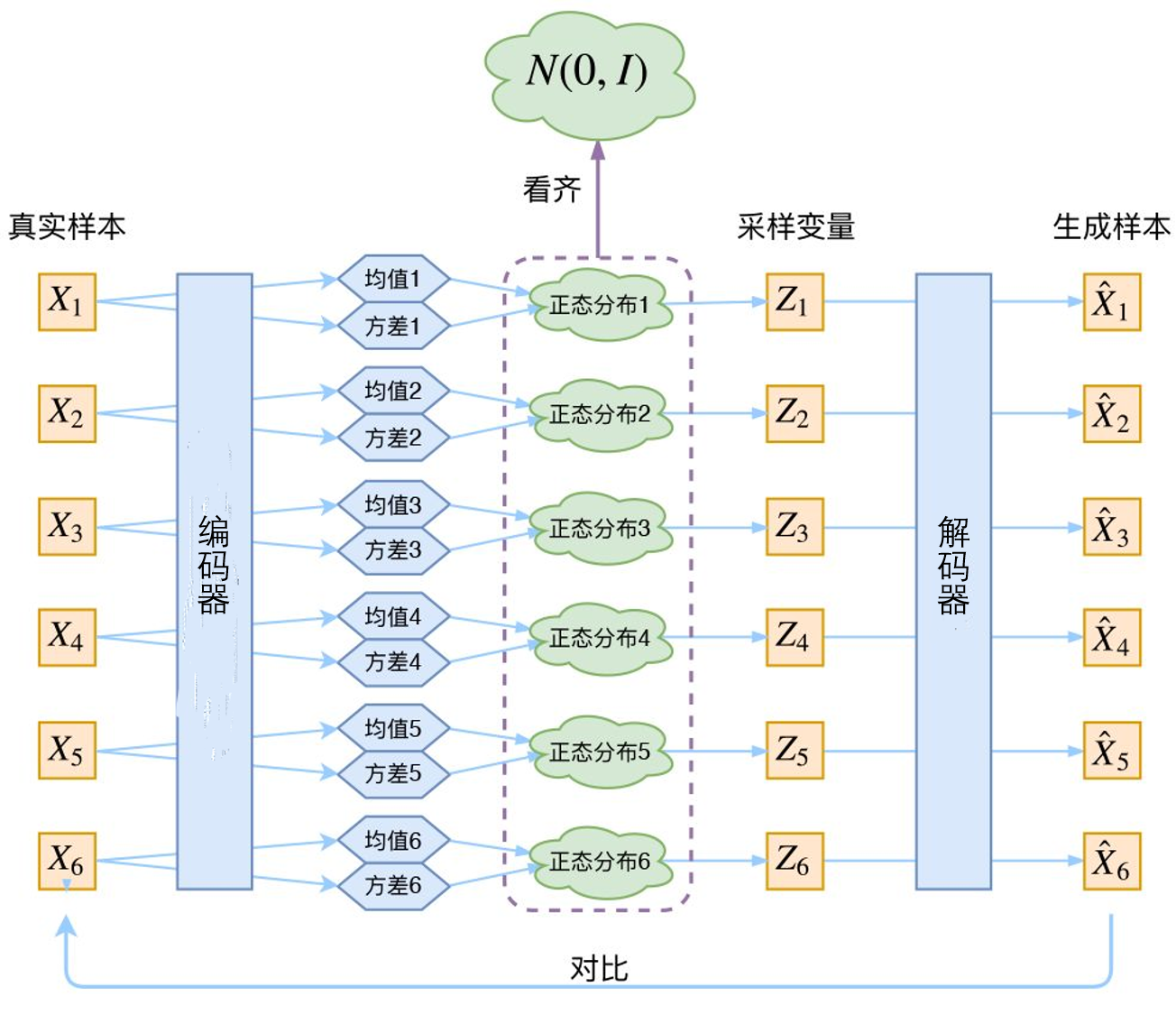

图卷积 变分 自编码器 Gae And Vgae 派大星1号 博客园

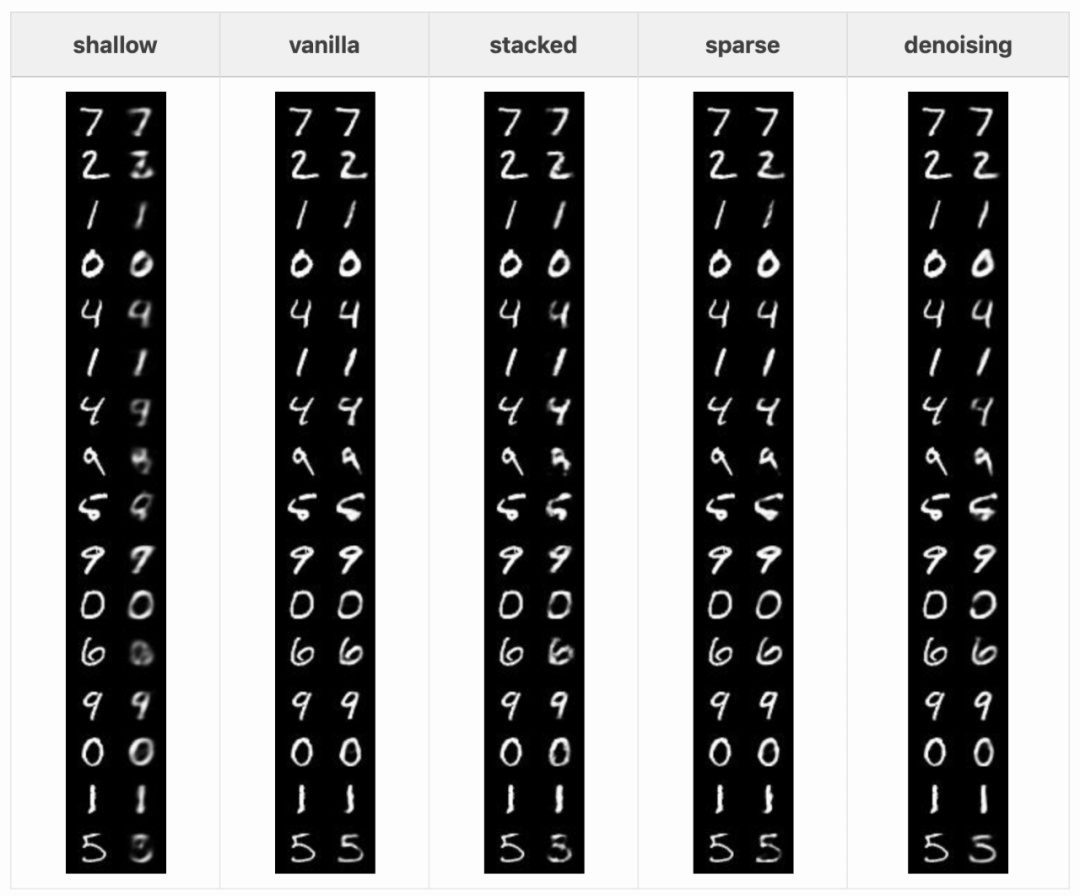

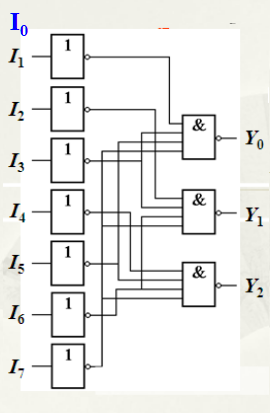

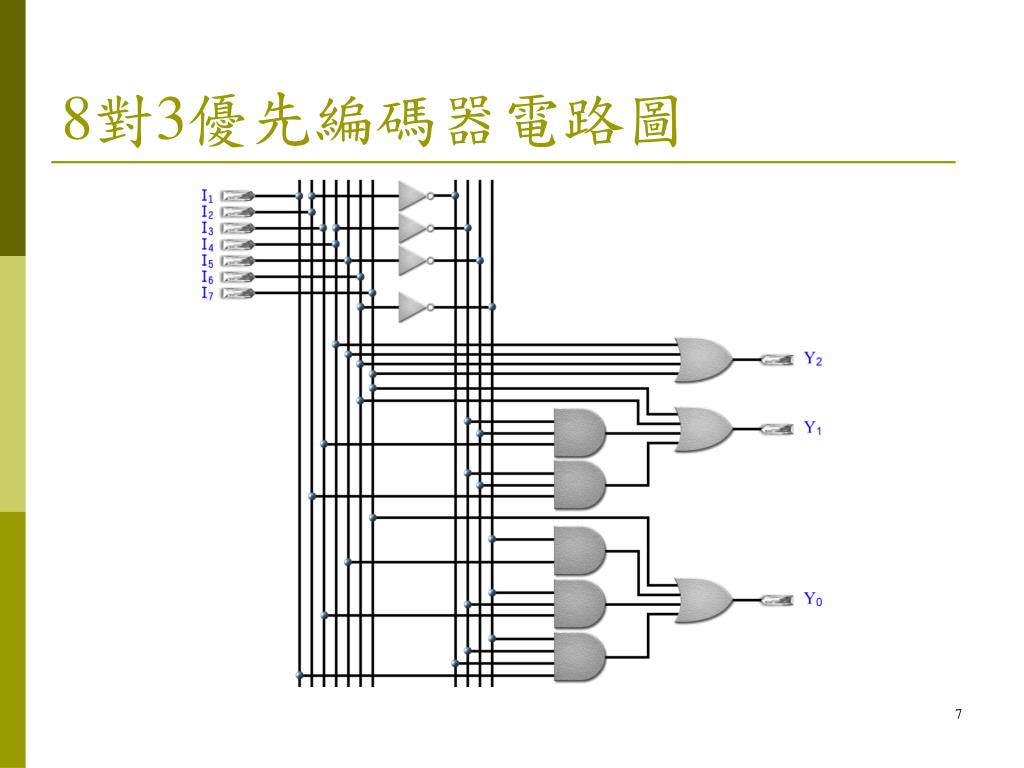

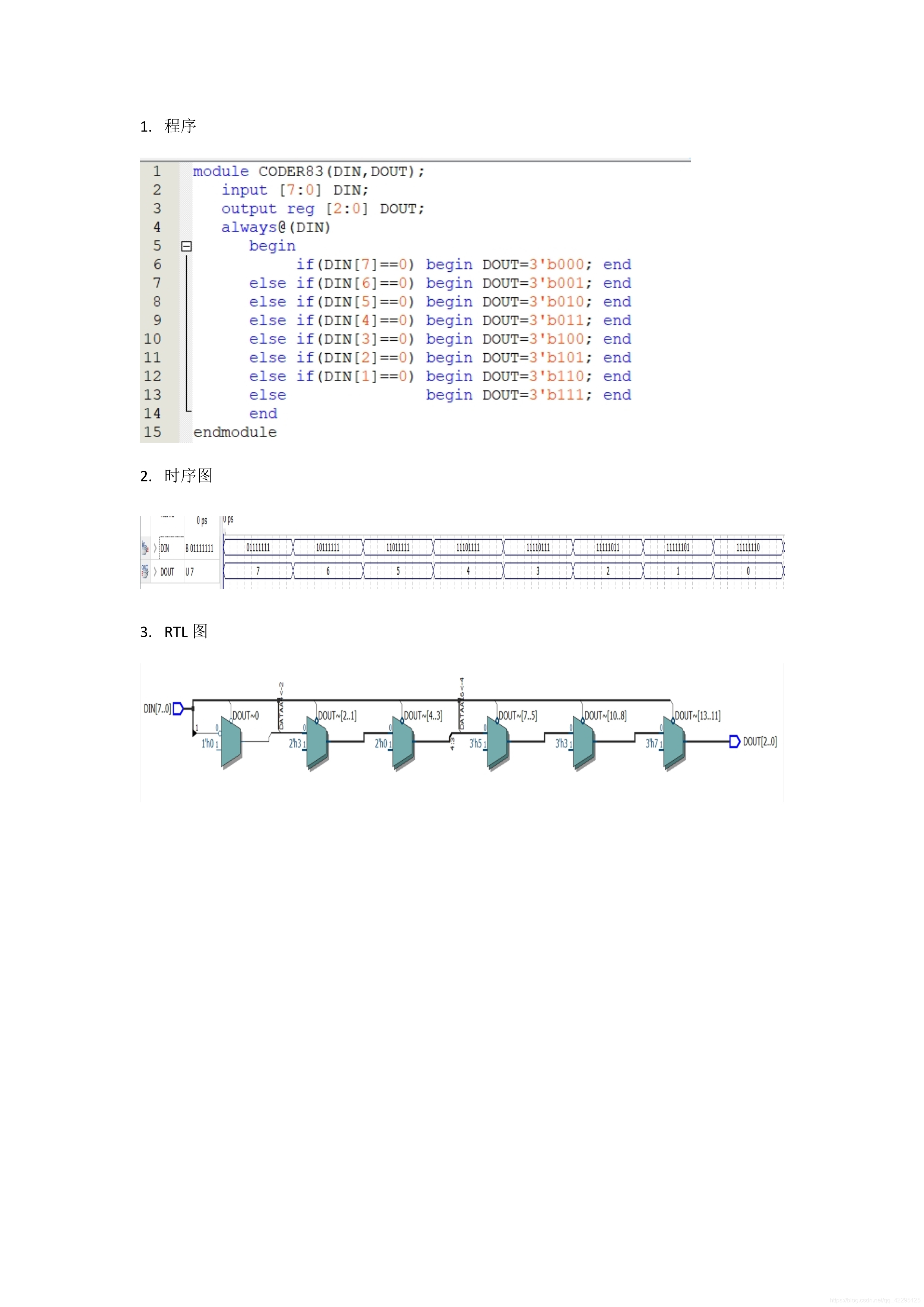

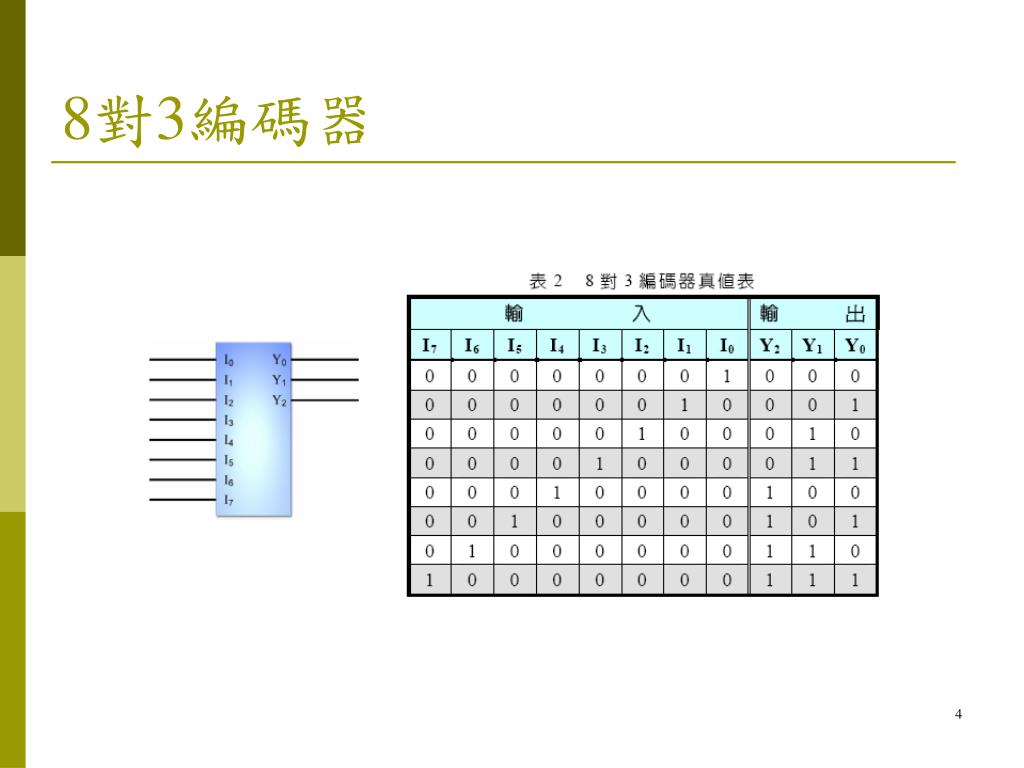

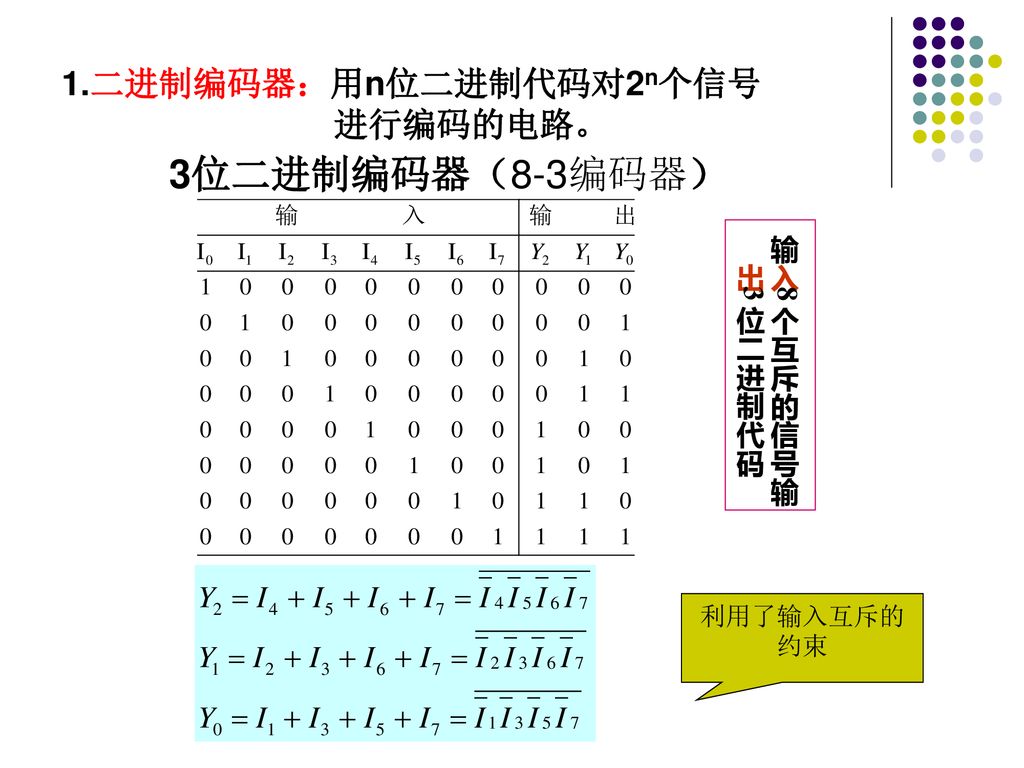

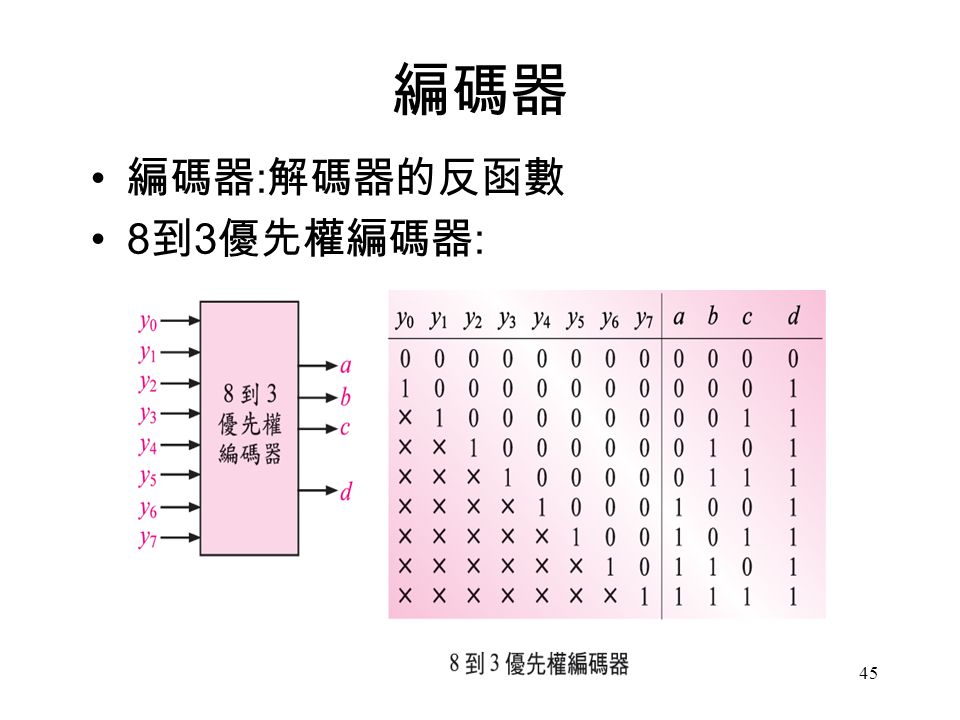

8对3编码器

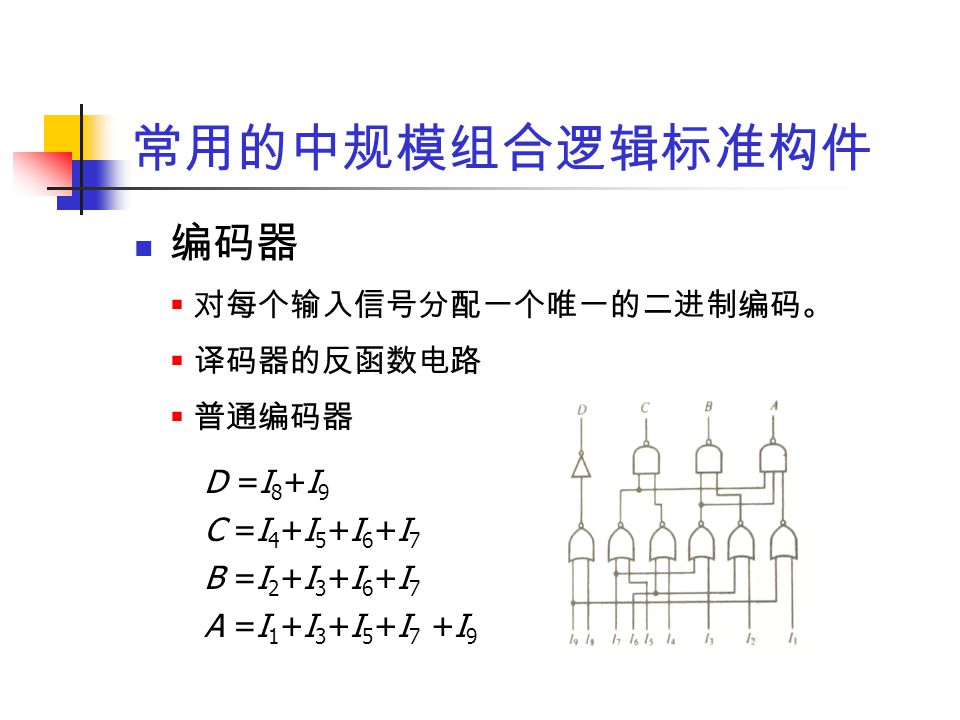

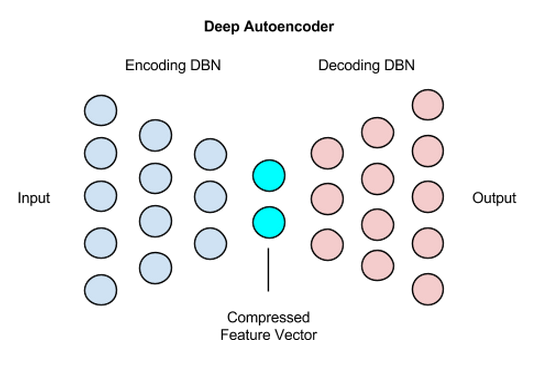

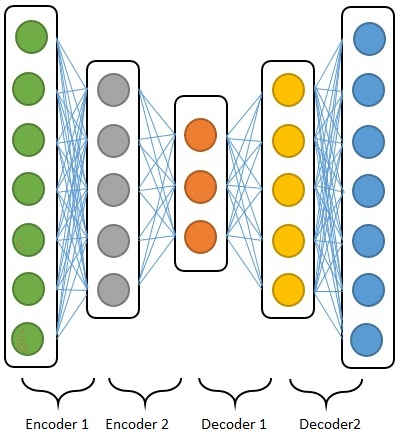

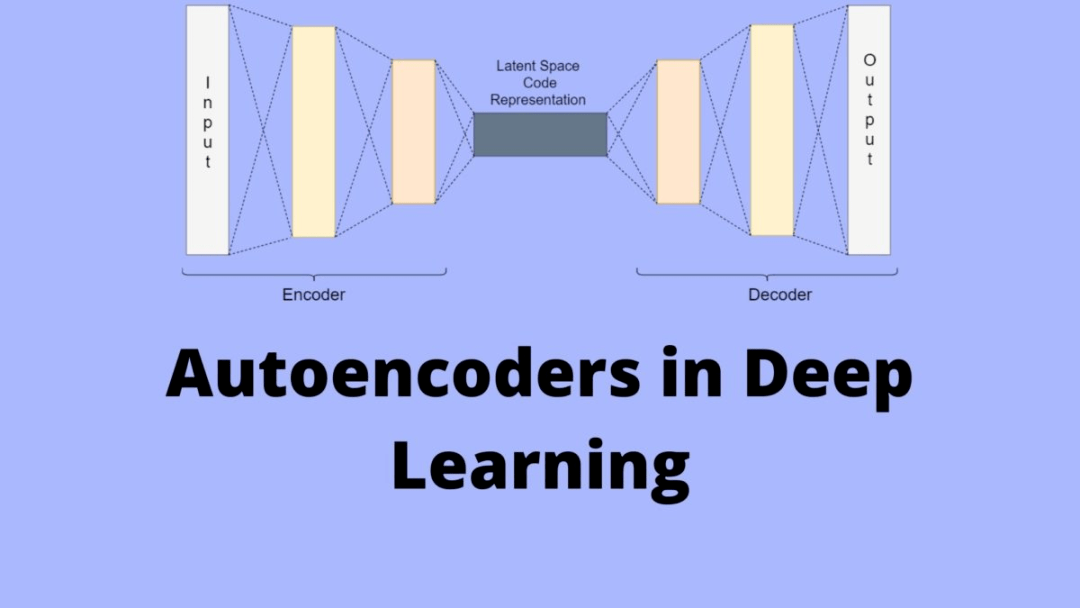

8对3编码器- 34 在实验箱上实现 优先编码器 首先设置八三优先编码器器下载板芯片引脚,如下图所示 图32 引脚设置示意图 试验箱各部分导线链接完毕后开始向实验箱烧录程序,如下图所示 图33 程序烧录示意图 如上图所示程序已经成功烧录进芯片中,下面开始在实验箱上实现 编码 器的功能。 在深度学习中,自动编码器是一种无监督的神经网络模型,它可以学习到输入数据的隐含特征,这称为编码 (coding),同时用学习到的新特征可以重构出原始输入数据,称之为解码 (decoding)。 从直观上来看,自动编码器可以用于特征降维,类似主成分分析PCA,但是其相比PCA其性能更强,这是由于神经网络模型可以提取更有效的新特征。 除了进行特征降维,自动编码器学习

电子入门基础知识之 8 3优先编码器 模拟数字电子技术

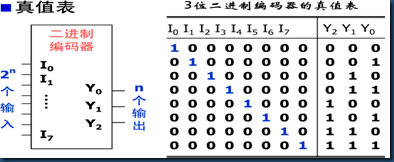

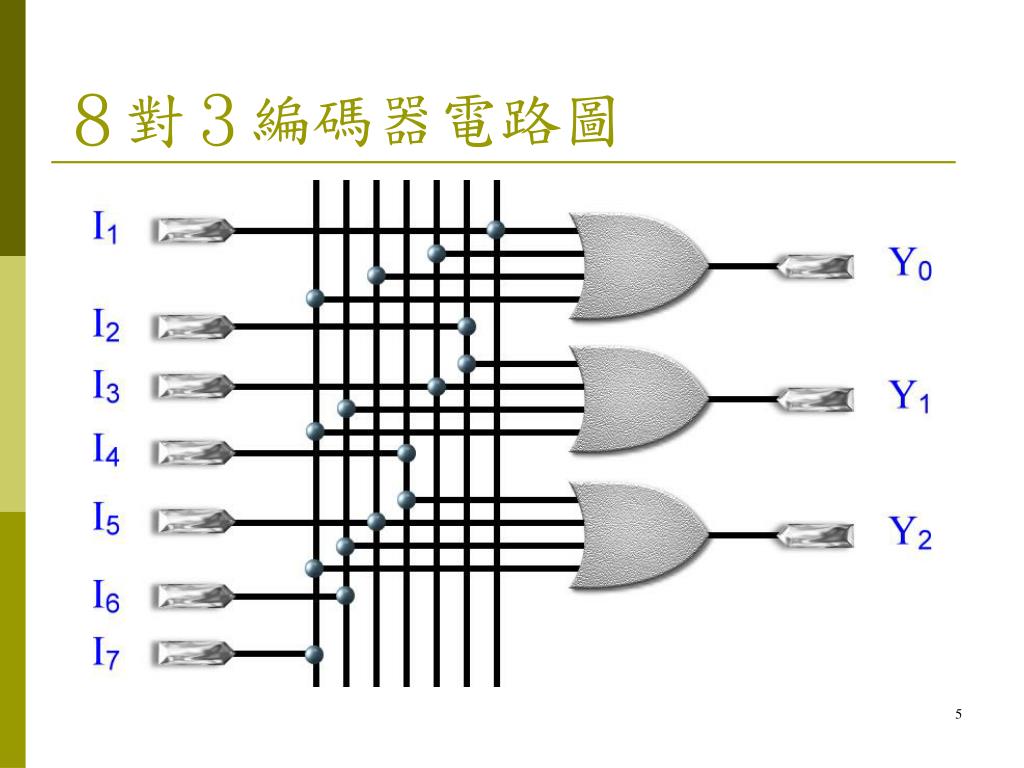

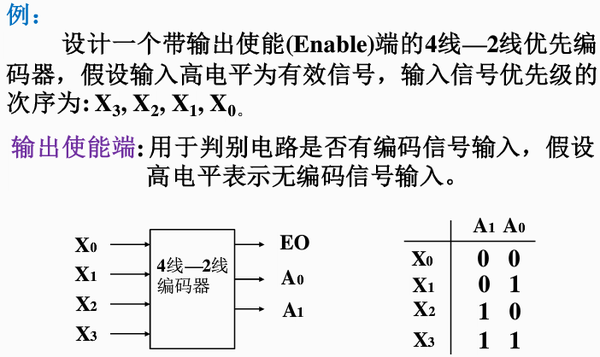

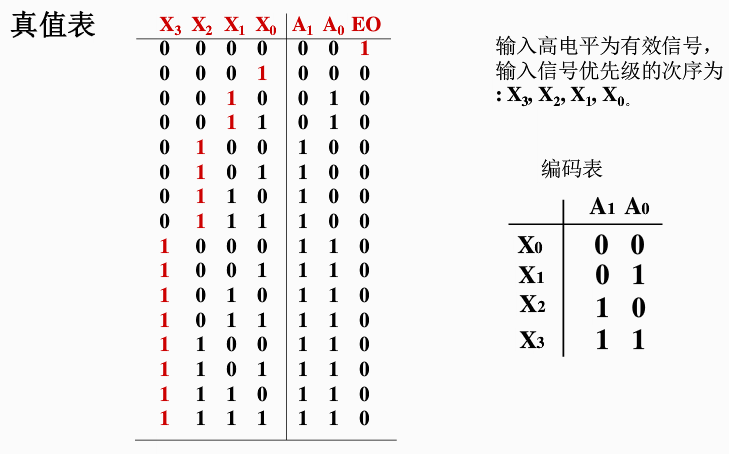

要避免此类干扰情况的出现,现场的编码器应由特定的工作电源独立供电,并且在输出功率选择上需做到足够大(编码器标示功耗的2倍以上);同时,选择的编码器应具有宽工作电压,例如 9~30Vdc 甚至 5~30Vdc 的工作电压,这表明编码器内部电路对工作电源的编码器 :实现编码的数字电路,把输入的每个高低电平信号编成一组对应的二进制代码。 设计一个输入为8个 高电平有效 信号,输出代码为原码输出的3位二进制编码器。 化简逻辑表达式: 由逻辑表达式可以得出,普通的编码器用或门即可实现。 对应的verilog程序如下: module mb_ (x,y);URL在线编码解码工具(UrlEncode编码 和 UrlDecode解码) UrlEncode编码 UrlDecode解码 复制加密后的网址 广告 URL在线编码解码工具 1,本功能实现将Url进行:UrlEncode编码 和 UrlDecode解码 2,对Url进行编码后可以将一些特殊字符和汉字变为Encode编码格式

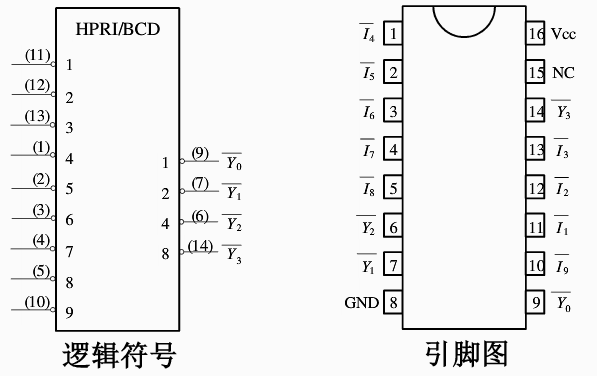

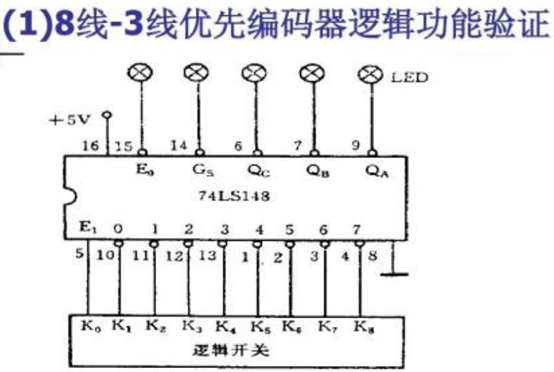

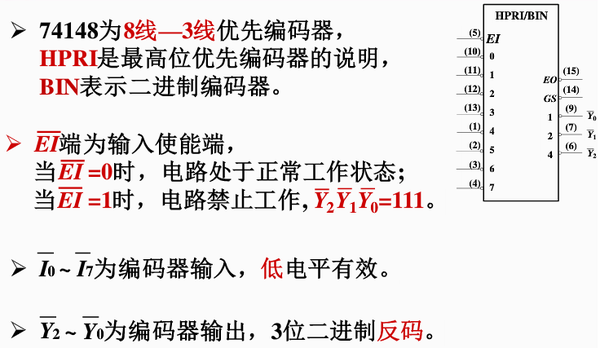

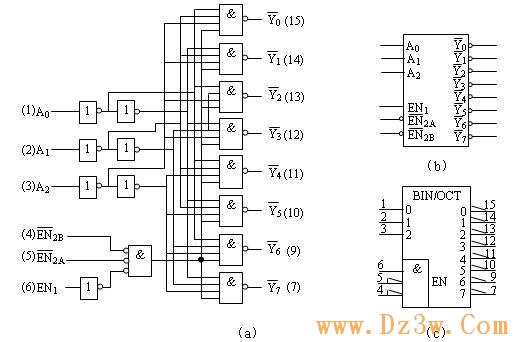

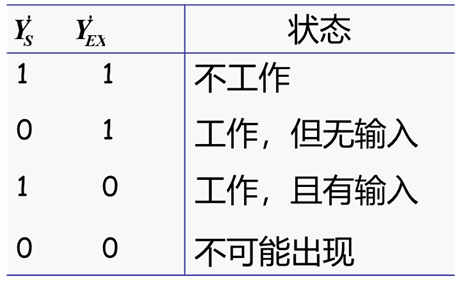

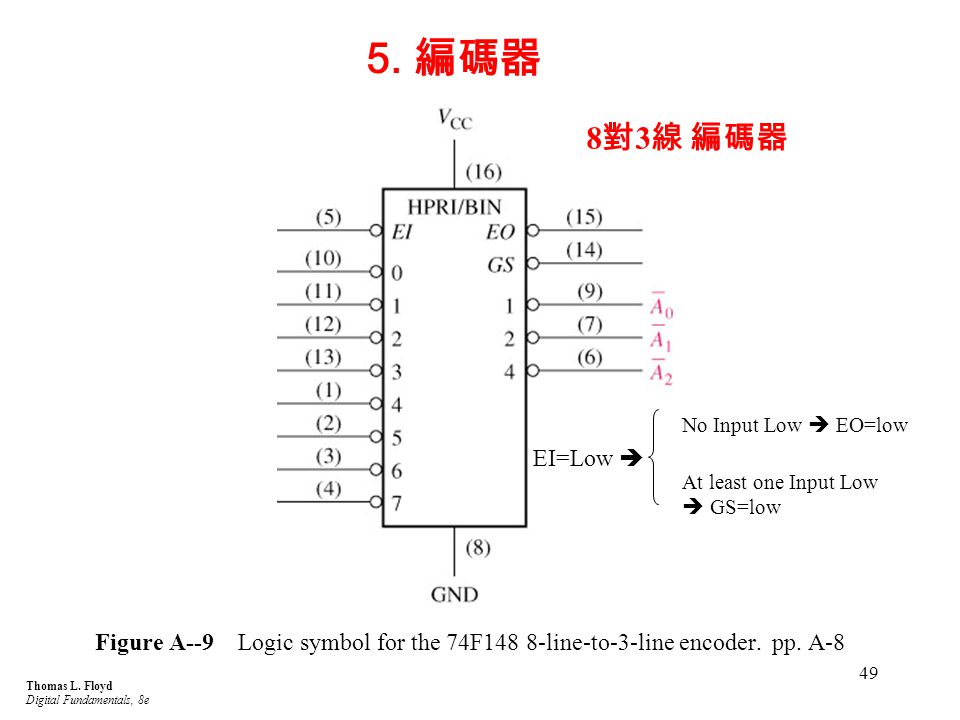

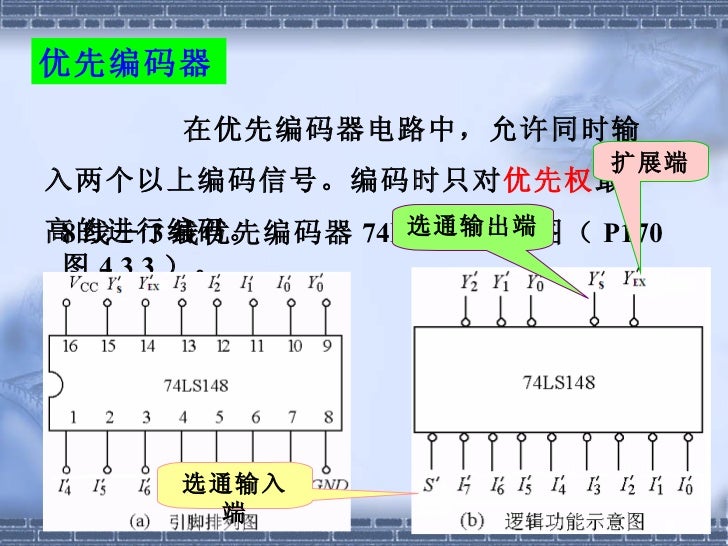

74ls147 引脚图管脚图和功能真值表优先 编码器 是当多个输入端同时有信号时,电路只对其中优先级别最的输入信号进行 编码 。 常用的集成优先 编码器 IC有10 线4线、8线3线两种。10线 导语: 74LS148是带有扩展功能的线优先编码器,它有8个信号输入端,3个二进制码输出端,一个输入使能端,一个选通输出端和一个扩展端。 使能端为"0"时,该芯片被选中,否则不被选中。 选通输出端和扩展端主要用于功能扩展。 74LS148是带有扩展功能的线优先 编码器 ,它有8个信号输入端,3个二进制码输出端,一个输入使能端,一个选通输出端和一个扩展端?>> 74ls148是8线3三线优先级编码器,其引脚图以及工作原理如下 74LS48是输出高电平有效的7段显示译码器,其引脚图以及工作原理如下 优先编码器的74HC148 ?>> 在优先编码器电路中,允许同时输入两个以上编码信号不过在设计优先编码器时,已经将所有的输入信号按优先顺序排了队在同时存在两个或两个以上输入信号时

74ls147和74ls148 有什么区别 : 74ls147和74ls148是两个截然不相同的芯片74ls147是10线 4线优先编码器,74ls148 是8线 3线八进位优先编码器优先编码器的功能允许同时在几个输入端有输入信号,编码器按输入信号排定的优先顺序,只对同时输入的几个信号中优先权最高的一个进行编码在优先编码器电路中,允许同时输入两个以上编码信号不过在设计优先编码器时,已经将所有的输入编码器用来分析输入序列,解码器用来生成输出序列。 图108描述了使用编码器—解码器将上述英语句子翻译成法语句子的一种方法。在训练数据集中,我们可以在每个句子后附上特殊符号""(end of sequence)以表示序列的终止。编码器每个时间步的输入依次 为什么要编码? 如果一样东西需要编码,那说明它不适合传输,原因有多种(有些字符有歧义、包含隐私数据、Size过大)。 在 URL 中,之所以要编码,是因为有些字符会引起歧义。比如参数中的key=value键值对,当value里含有= & ?

8 3线优先编码器74ls148的级联分析 电子发烧友网

数字电路编码器

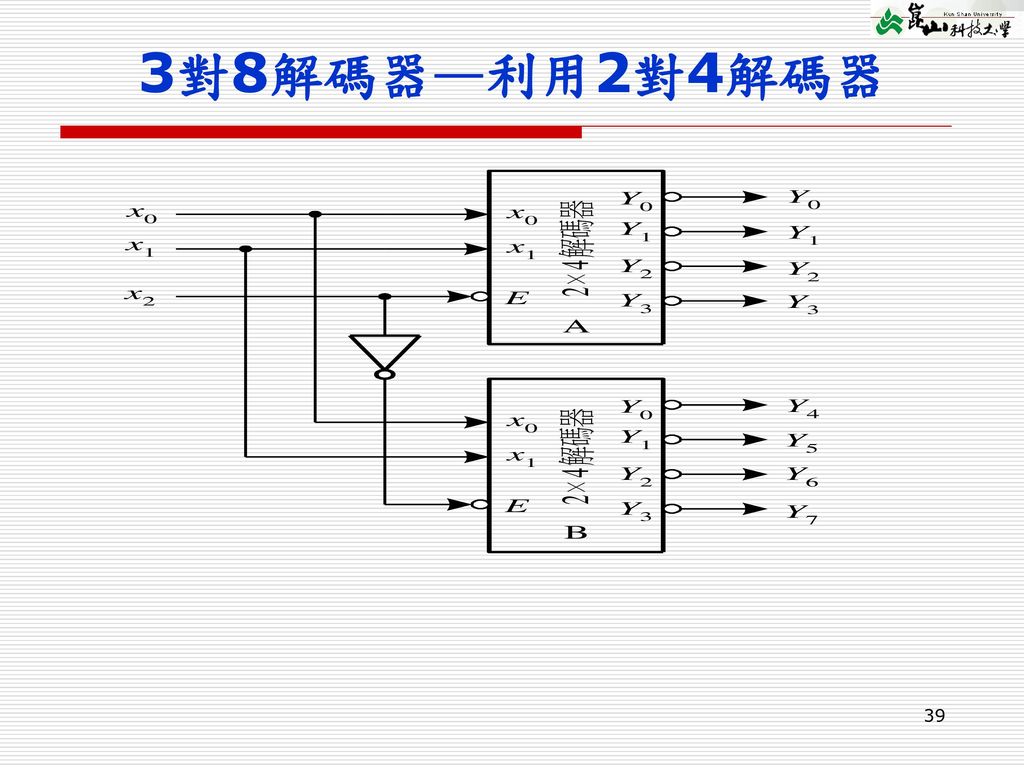

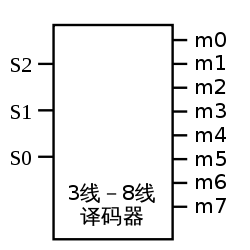

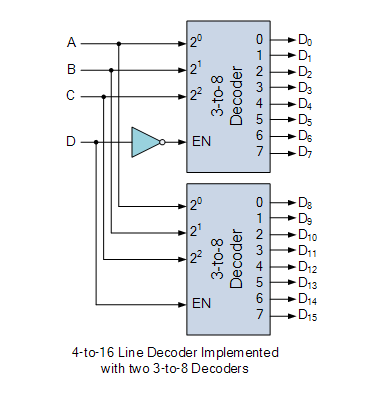

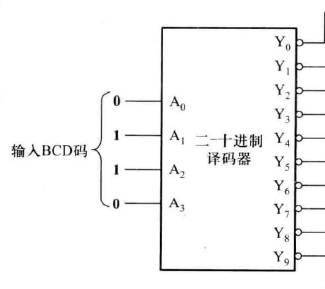

CD4532在Multisim中怎么找出来 在线等—— 会对人体就如同房管局美女人体房管局的人 望采纳 multisim中有哪些优先编码器 —— 10线4线优先编码器74LS147(TTL)、74HC147(CMOS),8线3线优先编码器74LS148(TTL)、74HC148(CMOS)、4532(CMOS) 数字电路逻辑设计中的是什么 _____ 是二进制译码器,3个数据输入、8个数据输出、3个芯片选择输入端子芯片有效时(片选),输出端子有效的一位就是输入值的译码值,如输入001,Y1=0,其余输出全为1,138是低电平有效138的片选有3个,使用起来比较灵活138是学习数字电路的基本器件,早期叫做地址译码 使用编码器74ls147,如何进行对十进制数0编码 : 图1245 二—十进制优先编码器74ls147的逻辑图 二—十进制优先编码器 二 十进制编码器74ls147的功能表中输出是按照反码

數位邏輯學 第八章

Tensorflow学习笔记 自编码器及多层感知器 战争热诚 博客园

、元件说明及相关计算31 元件说明 311、优先编码器 优先编码器既在同一时间内,当有多个输入信号请求编码时,只对优先级别高的信 号进行编码的逻辑电路,称为优先编码器。常用的集成优先编码器有74ls148(8 线-3 线)和74ls147(10 线-4 线)两种制式。怎么用4片8—3线74hc148优先编码器组成一个32—5线 : 74ls148芯片是8线3线优先编码器如果要得到32线5线优先编码器,可以通过列单块74ls148芯片的简化真值表,列32线5线优先编码器的简化真值表,找出32线5线优先编码器的每一个输出与每块74ls148的扩展端yex的关系,与每块74ls148输出的关系利用74lsl148的选通输入端s、选通输出端ys、扩展端yex就可用四块74ls148芯片构成32线5线优1、512线编码器33V:工作电压为 33V 2、512线编码器5V:工作电压为 5V 3、新版编码器用于 C车,D车,F车 时需要将车模上的安装孔磨大一些 就可以了。 (介意者请拍老版编码器) 本专利产品购买福利:终身维修服务,买一个用终身,一分价钱一分货

8 3线优先编码器74ls148的级联分析 电子发烧友网

数字电路编码器

集成电路74LS147有什么功能 : 74LS147是 10线 4线优先编码器 10线的十进位编码成8421 BCD码四线 74ls147和74ls148 有什么区别 : 74ls147和74ls148是两个截然不相同的芯片74ls147是10线 4线优先编码器,74ls148 是8线 3线八进位优先编码器优先编码器的功能允许同时在几个输入端有输入信号,编码器按输入信号排定的优先顺序,只对同时输入的几个信号中优先权最高的一个进行编码电脉冲编码器的i,@才可对测量系统进行补偿c同时 为具体确定对应的* ,%i,@必须以m相零位脉冲作为 采样控制脉冲@以保证从零位脉冲开始计数c?cn 光电 脉冲编码器 宽比例系数的标定 采用h'op5jcq型光电编码器rqs电源和台 湾研华公司提供的tuvw'定时j计数卡c该卡采 数字逻辑电路学习总结 学 姓 学 专 号: 名: 院: 业: 、 数字逻辑电路学习总结 经过一学期的学习,我对数字逻辑电路这门课程总结如下: 一:数字逻辑电路绪论及基础 1.数字信号与模拟信号的区别(数值和时间的连续性与不连续性) 2.数字电路特点电路结构简单,便于集成化;工作可靠

Verilog Hdl 之8 3编码器 可编程器件 面包板社区

2

原因是:服务器对响应编码和浏览器对响应解码所使用的编码都是相同的,为responsesetCharacterEncoding—contentType指定的编码,而浏览器对请求参数的编码 和 服务器对请求参数解码 所使用的编码如果不一致,就会造成乱码 ③对中文解码,无论使用什么解码方式Output 2 0y; 最近改用sublime编辑器,我下载了一个汉化版的。今天在sublime写代码显示的中文是正常的(在sublime编辑器打开没问题,估计是之前加了安装包: CtrlShiftP → Package Control Install Package →ConvertToUTF8),但是在浏览器打开中文就出现乱码。以下是我的解决方法:在打开的文件中输入 "default_encodi

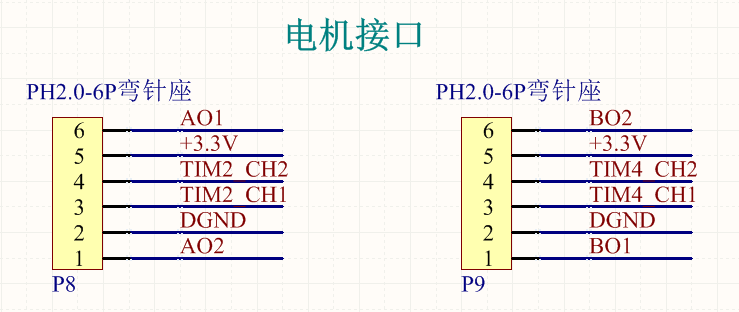

电机控制基础3 定时器编码器模式使用与转速计算

长文详解 从transformer到bert模型

增 量 型 编 码 器 (旋转型) 工作原理 由一个中心有轴的光电码盘,其上有环形通、暗的刻线,有光电发射和接收器件读取,获得四组正弦波信号组合成A、B、C、D,每个正弦波相差90度相位差(相对于一个周波为360度),将C、D信号反向,叠加在A、B两相上,可增强稳定信号;另每转输出一个Z相脉冲以代表零位参考位。 由于A、B两相相差90度,可通过比较A相在前还是B相在前《数字电子技术》课程进一步解释窗口 进一步解释 可通过常用集成芯片二十进制优先编码器74ls147的逻辑图来理解优先编码的实现原理图1245 二—十进制优先编码器74ls147的逻辑图 二—十进制优先编码器74ls147的逻辑图如图1245Always@ (x) begin case (x) 8'by=3' b000;

电子入门基础知识之 8 3优先编码器 每日头条

8 3编码器 3 8译码器的verilog实现 Sasha Xu 博客园

为了提升 UTF8 编码检测的可靠性,Microsoft 发明了一种 UTF8 变体形式 (Python 25 称之为 "utf8sig") 专门用于其 Notepad 程序:在任何 Unicode 字符在被写入文件之前,会先写入一个 UTF8 编码的 BOM (它看起来是这样一个字节序列 0xef, 0xbb, 0xbf)。 由于任何字符映射编码后的文件都不大可能以这些字节值开头(例如它们会映射为Reg 2 0y;可以用于对 JSON 浮点数使用其它数据类型和解析器 (比如 decimalDecimal )。 parse_int ,如果指定,将与每个要解码 JSON 整数的字符串一同调用。默认状态下,相当于 int(num_str) 。可以用于对 JSON 整数使用其它数据类型和语法分析程序 (比如 float )。

编码器和译码器 数电实验报告 Overwhelmed的博客 Csdn博客 编码器和译码器

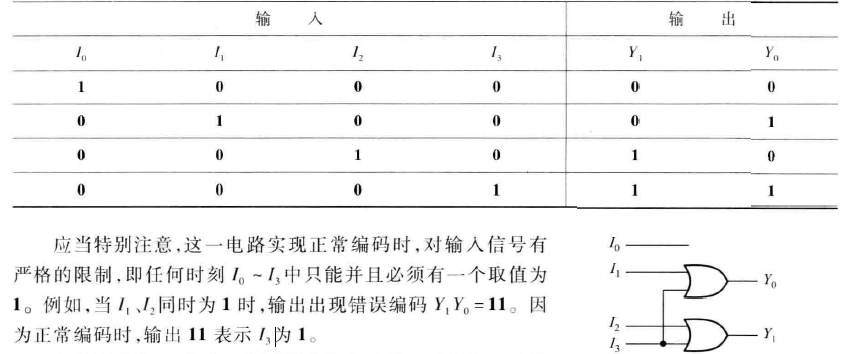

第二章组合逻辑梁华国计算机与信息学院计算机系统结构研究室workroom Socweb Index Php Ppt Download

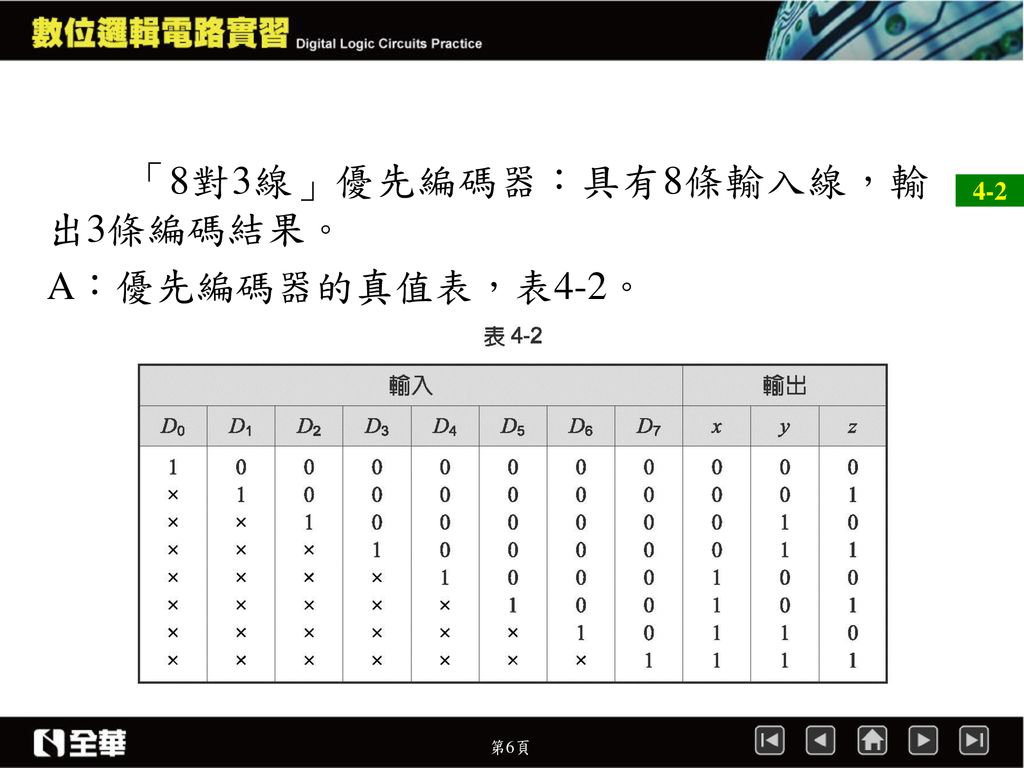

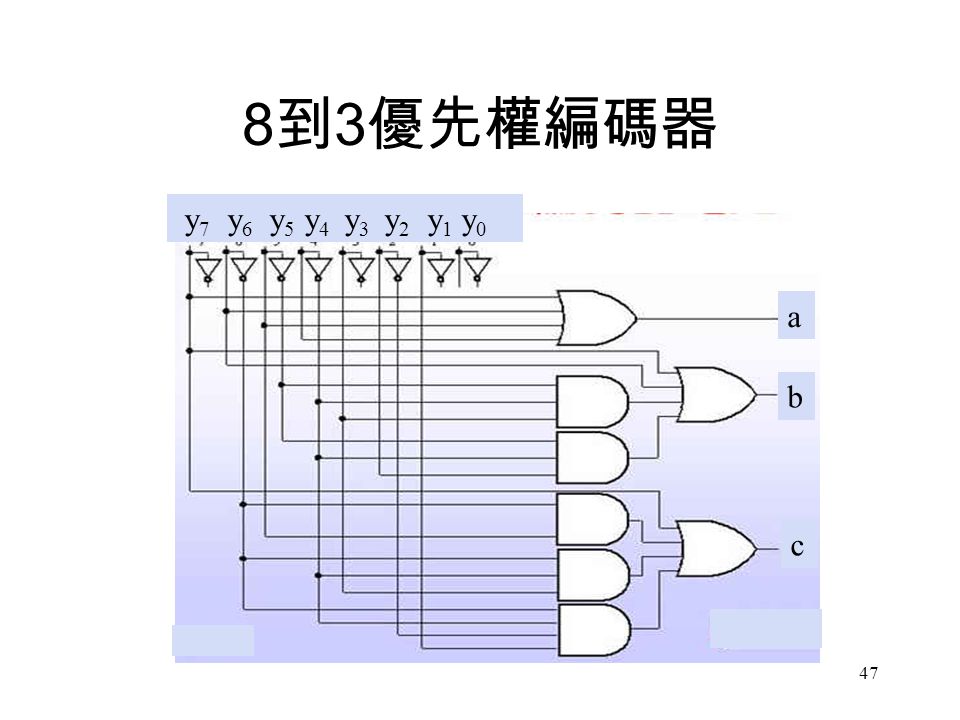

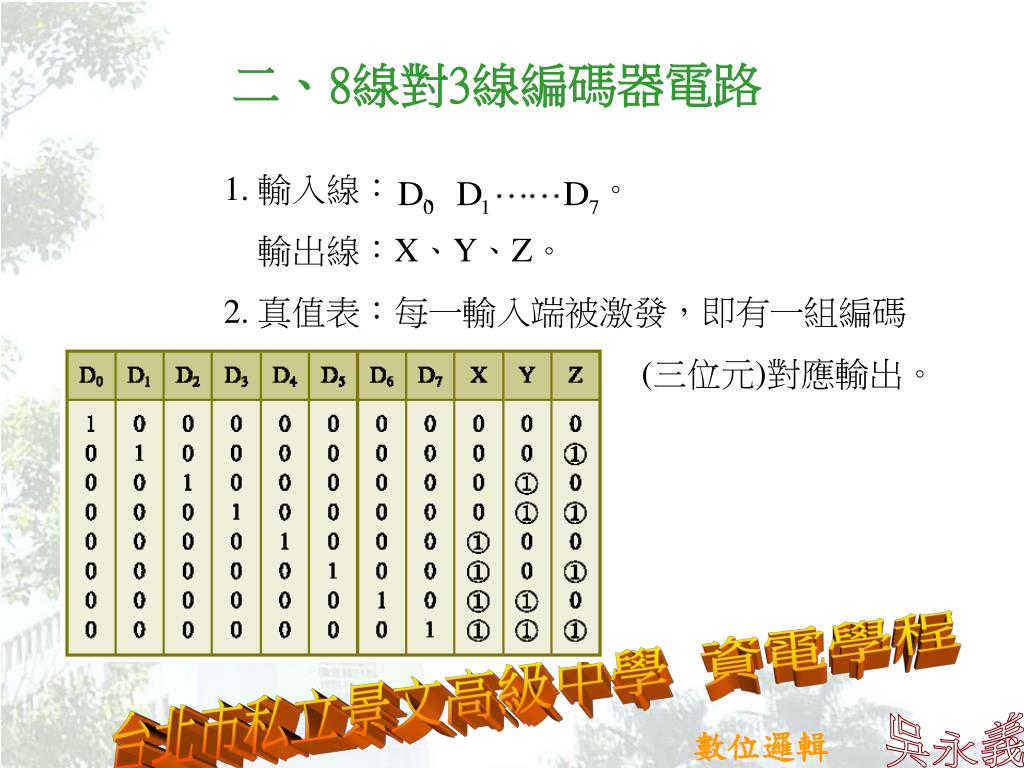

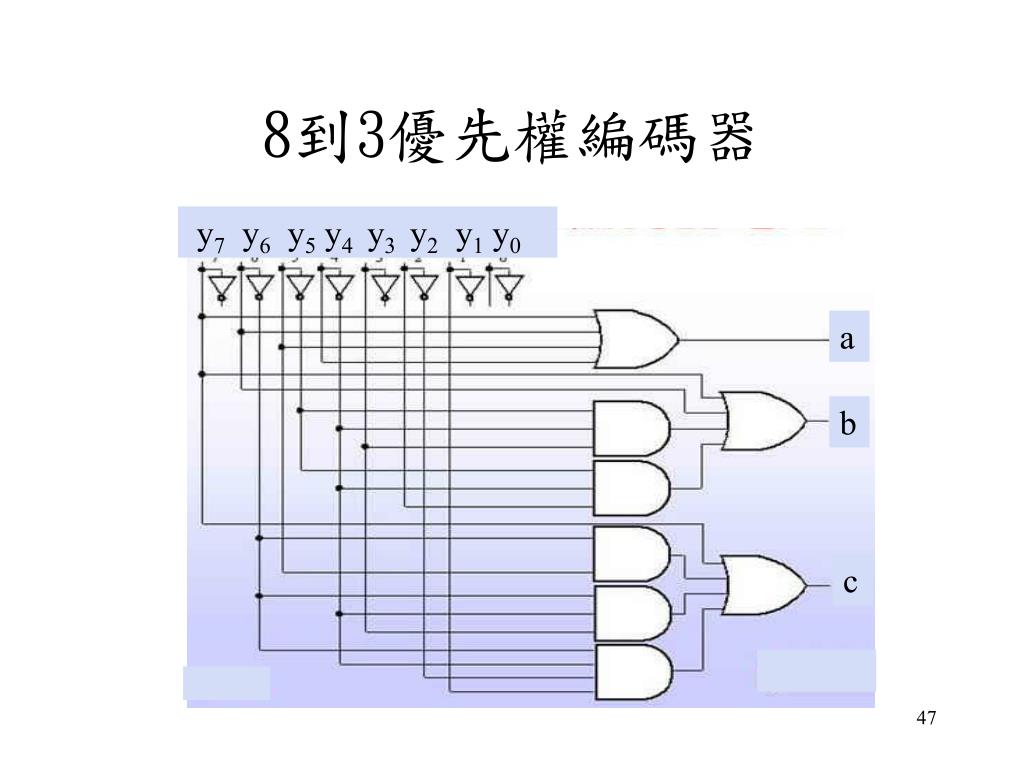

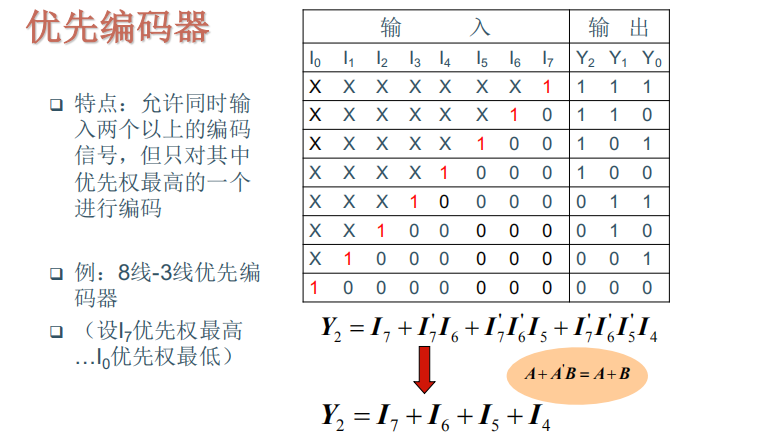

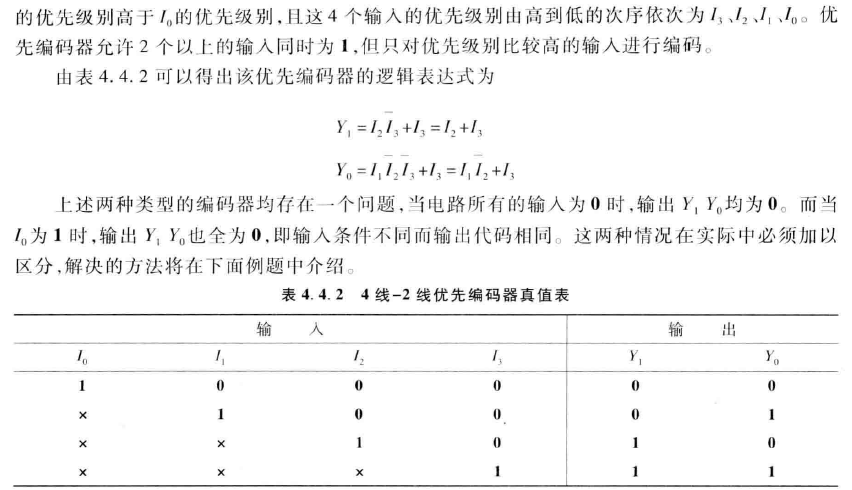

优先级编码器有许多不同的形式,例如一个8输入优先级编码器及其真实值表,如下所示。 8至3位优先编码器 优先级编码器以标准ic形式提供,而ttl 74ls148是8位至3位优先级编码器,具有八个活动的low(逻辑" 0")输入,并在其输出处提供输入最高等级的3位代码。编码器线 高柔屏蔽电缆2对3对4对5对4芯芯6芯8芯10芯伺服编码器线 编码器脉冲信号走的是高频,在选择电缆内芯时需要根据高频特性参数来选择电缆内芯的平方面积,而不是根据平方面积来选择电缆。 当机器脉冲信号传输在米以上时,必须选用编码器专用信号 cd4532可以用什么芯片代替 —— cd4532是8线3线优先编码器,可以用74ls148代替,但不能2113直接代替,因两个芯片的引脚功能5261有些差异,更主要是两者的工作电压是不同4102的,cd4532电源1653电压可达15v,而74ls148是5v,如果电源电压就是5v,就可以了代替时,内上百度文库下载这两个芯片的资料,容看清楚各自的引

Response解决中文输出乱码问题 Request解决请求参数的乱码问题 牛客博客

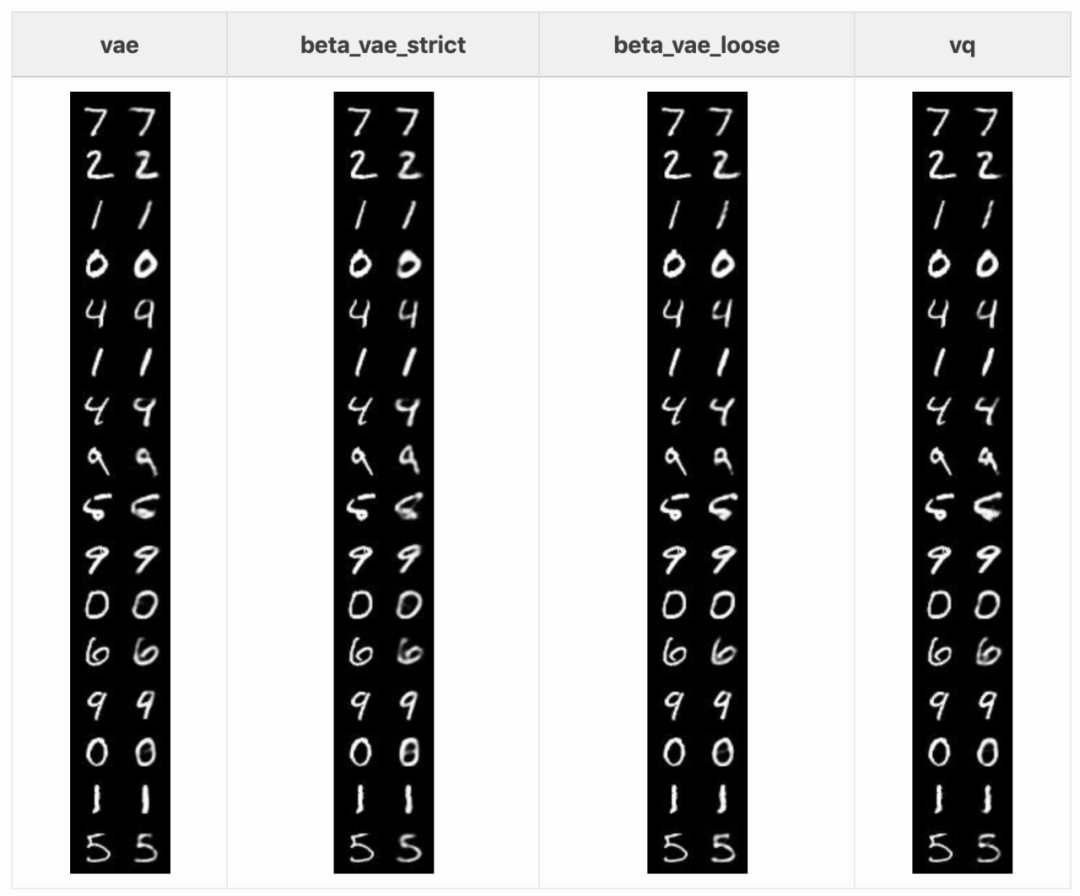

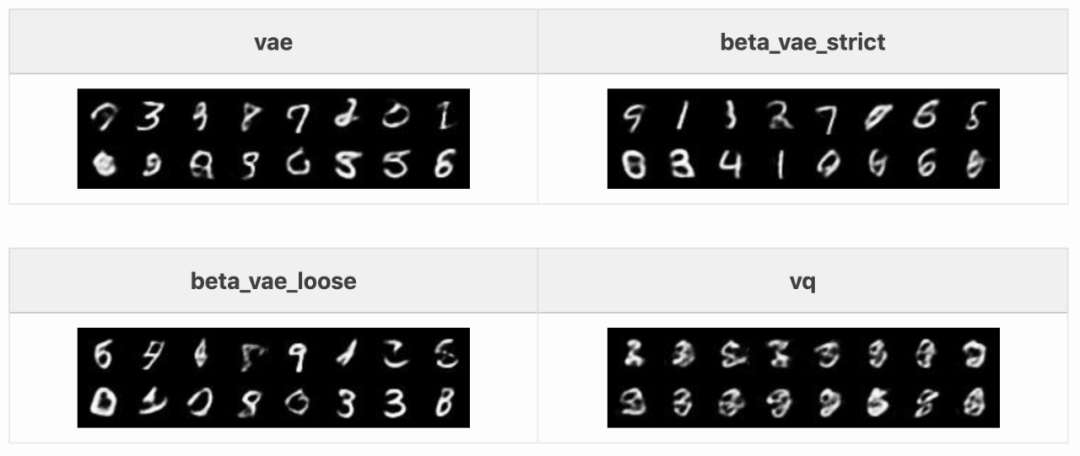

无监督训练用堆叠自编码器是否落伍 Ml博士对比了8个自编码器 深度

Verilog HDL 之 编码器 原理: 在数字系统中,常常需要将某一信息(输入)变换为某一特定的代码(输出)。把二进制码按一定的规律排列,例如8421码、格雷码等,使每组代码具有一特定的含义(代表某个数字或是控制信号)称为编码。 优先编码器课程设计doc,东北石油大学课程设计任务书 课程 硬件课程设计 题目 优先级编码器设计 专业 计算机科学与技术 姓名 学号 主要内容、基本要求等 一、主要内容: 利用EL教学实验箱、微机和QuartusⅡ软件系统,使用VHDL语言输入设计。1 杨刚,龙海燕现代电子技术VHDL与数据系统设计 (5)具有手动和自动清零功能 使用编码器74LS147,如何进行对十进制数0编码 ?>> 1 半导体类型a本征半导体b掺杂半导体 性质热敏性,光敏性,掺杂性2 PN结具有单向导电性,加正电压(正向偏置),导通,电荷区变宽3 单晶硅中加砷或磷形成N型,空穴为多子,自由电子少子3

2

Ppt 第4 章编码器与译码器coder And Decoder Powerpoint Presentation Id

: 74ls148是8线3三线优先级编码器,其引脚图以及工作原理如下 74LS48是输出高电平有效的7段显示译码器,其引脚图以及工作原理如下 总结74ls148编码电路的功能 : 74LS148集成电路是一个典型的优先编码器,在优先编码器电路中,允许同时输入两个以上编码信号不过在设计优先编码器时,已经将所有的输入信号按优先顺序排了队编码器和译码器原理 一、二进制编码器 用 n 位二进制代码对 N = 2n 个信号进行编码的电路 编码表 1 3 位二进制编码器(8 线 3 线) I0 Y2 输 出 I1 输 入 I2 两台电机编码器出线的颜色是一样的 按照相同的接线 ecmac604rs可以用 ecmac604rs不可以用 且 伺服驱动器报警 al011 (位置检出器异常) 伺服驱动器是asdab2

连载 Fpga Verilog Hdl 系列实例 8 3优先编码器 让linux飞一会儿 博客园

图卷积 变分 自编码器 Gae And Vgae 派大星1号 博客园

8线3线编码器有几个输入,几位二进制代码输出 7 vhdl 8线3线优先编码器 1 EDA课程设计报告8线3线优先编码器 先简单介绍一下什么是"线优先编码器": 线优先编码器由9个输入端和五个输出端组成,允许同时在几个输入端输入信号。 当有多个输入信号传入时,只对其中优先权最高的一个输入信号进行编码(输出的二进制代码以反码形式表示) 如图所示: 因此,我们可以进行实体定义: 定义八个输入端(由权低到权高):a,b,c,d,e,f,g,h 定义一个选通输入端(0时才正常工作

Ppt 數位邏輯實習powerpoint Presentation Free Download Id

8 3编码器 3 8译码器的verilog实现 Sasha Xu 博客园

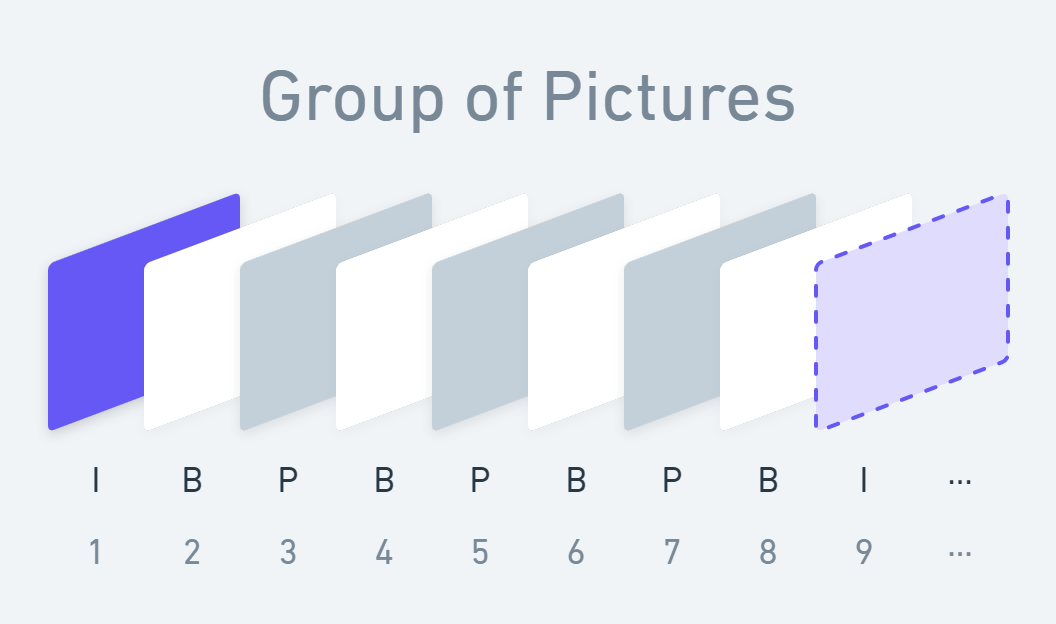

视频帧名词解释 Webrtc 学习指南

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

编码器 常用中规模集成电路 Msi 数电 知乎

Cna Rs编码器的编码方法及rs编码器 Google Patents

二 相關知識在數位系統中 資料的表示方式通常是以0與1這兩種基本型態組合而成的 資料若要作處理 則必須將它轉為處理單元所能接受的型式 碼 此即所謂的 編碼 Encode 可以完成此編碼工作的電路稱為編碼器 Encoder 而當處理單元將資料處理完之後 則必須將它呈現

6 4 1 74ls148编码器介绍

电子入门基础知识之 8 3优先编码器 模拟数字电子技术

Usb3 0中8b 10b编解码器的设计 电子发烧友网

組合邏輯的函數functions Of Combination Logic Ppt Video Online Download

数电三 编码器和译码器 半个月儿上来的博客 Csdn博客 编码器和译码器

Ppt 吳永義powerpoint Presentation Free Download Id

电子入门基础知识之 8 3优先编码器 模拟数字电子技术

Ppt 組合邏輯的函數functions Of Combination Logic Powerpoint Presentation Id

数字电路笔记 摸黑干活

译码器 维基百科 自由的百科全书

译码器工作原理 译码器逻辑功能 译码器应用 与非网

数字电路基础那些事1 组合逻辑 从译码器到编码器 三点羊羽 博客园

數位邏輯設計與實習ch04 組合邏輯電路設計 Ppt Download

自编码器autoencoder 王敏的博客

数电三 编码器和译码器 半个月儿上来的博客 Csdn博客 编码器和译码器

Ppt 數位邏輯實習powerpoint Presentation Free Download Id

自编码器autoencoder 王敏的博客

编码器和译码器 数电实验报告 Overwhelmed的博客 Csdn博客 编码器和译码器

如何用verilog Hdl来实现编码器 Susugreen 的博客 程序员宅基地 Verilog编码器 程序员宅基地

编码器 常用中规模集成电路 Msi 数电 知乎

數位電路設計 蕭宇宏 U07 組合邏輯電路 11 編碼器電路 Youtube

无监督训练用堆叠自编码器是否落伍 Ml博士对比了8个自编码器 深度

自动编码器一览 一 Kyon Huang 的博客

Cd4532 8 3线优先编码器以及应用 码农家园

Verilog Hdl学习 8 3编码器 长风弦歌的博客 Csdn博客 八三编码器verilog

数字电路基础那些事1 组合逻辑 从译码器到编码器 三点羊羽 博客园

增量编码器act50 A B 8 增量型编码器 华尔圣15年专注编码器制造

深度学习 自动编码器 对称网络结构 华为云

Ppt 數位邏輯實習powerpoint Presentation Free Download Id

译码器 维基百科 自由的百科全书

8 3编码器 3 8译码器的verilog实现 Sasha Xu 博客园

3 8解碼器74ls138中文資料 研發互助社區

电子入门基础知识之 8 3优先编码器 每日头条

算术编码 维基百科 自由的百科全书

逻辑电路知识 二进制解码器是什么 电子技术基础 面包板社区

编码器 常用中规模集成电路 Msi 数电 知乎

数字电路编码器

10 9 编码器 解码器 Seq2seq 动手学深度学习 文档

编码器和译码器 编码器和译码器实验目的熟悉中规模集成电路编码器 译码器的工作原理和逻辑功能掌握编码器 译码器的级联方法 了解编码器 译码器的应用 Ppt Download

编码器 常用中规模集成电路 Msi 数电 知乎

自动编码器一览 一 Kyon Huang 的博客

Hc4511与显示器接法下载 Ppt模板 爱问共享资料

8 3编码器 3 8译码器的verilog实现 Sasha Xu 博客园

74ls148逻辑图 万图壁纸网

基于verilog 的经典数字电路设计 4 编码器 新芯时代的博客 Csdn博客

定制定制兴大顶针型螺纹夹紧式联轴器编码器弹性联接器绕线式连轴器外径19 长23 孔3至8可选 图片价格品牌报价 京东

无监督训练用堆叠自编码器是否落伍 Ml博士对比了8个自编码器 深度

数字电子技术digital Electronic Technology 5 组合逻辑电路设计题解题技巧归纳 凝望 划过星空的博客 Csdn博客

Hello Fpga 编码器 译码器 数据选择器 数值比较器 加法器 每日头条

Www Cyut Edu Tw Yfahuang Chap04 Pdf

编码器 常用中规模集成电路 Msi 数电 知乎

无监督训练用堆叠自编码器是否落伍 Ml博士对比了8个自编码器 深度

编码器 电子工程世界

哔哩哔哩h 265编码器在直播和点播的实践和应用 哔哩哔哩

組合邏輯的函數functions Of Combination Logic Ppt Video Online Download

第十六讲编码器 电子常识 电子发烧友网

8 3编码器 3 8译码器的verilog实现 Sasha Xu 博客园

組合邏輯的函數functions Of Combination Logic Ppt Video Online Download

Digital System Design Weidong Wang College Of Information

变分自编码器解析 Knightboy 博客园

8 3线优先编码器74ls148的级联分析 电子发烧友网

编码器 常用中规模集成电路 Msi 数电 知乎

4 3 1 2 1优先编码器 腾讯视频

基于vhdl的旋转编码器接口电路的实现 可编程逻辑 与非网

數位邏輯學 第八章

数电三 编码器和译码器 半个月儿上来的博客 Csdn博客 编码器和译码器

16线4线编码器电路图 用两片74ls148优先编码器扩展为16 4线优先编码器 三人行教育网 Www 3rxing Org

第4章1

Timer编码器模式读取编码器 给新手的两轮自平衡小车开发实战指南

4d F736f F D c6a6ecc5debfe8b35dad70bb50b9eab2dfb3f8a769abcaadb1 Pdf 免费下载

数字电路编码器

8 3线优先编码器74ls148的级联分析 电子发烧友网

数字电路基础那些事1 组合逻辑 从译码器到编码器 三点羊羽 博客园

0 件のコメント:

コメントを投稿